Logique combinatoire

Dans ce chapitre nous nous intéressons à une famille de circuits logiques pour lesquels la sortie dépend uniquement des états des entrées.

1 - Addition binaire

a) Demi-additionneur

Addition et soustraction sont deux opérations arithmétiques de base. Commençons par l'addition de deux nombres binaires, la soustraction sera étudiée dans le prochain paragraphe. En base 2 l'addition de deux bits s'écrit :

Addition et soustraction sont deux opérations arithmétiques de base. Commençons par l'addition de deux nombres binaires, la soustraction sera étudiée dans le prochain paragraphe. En base 2 l'addition de deux bits s'écrit :

Comme en décimal, nous devons donc tenir compte d'une éventuelle retenue (carry). La figure 1 montre la décomposition de l'addition de deux nombres binaires de quatre bits.

L'addition des deux bits de plus bas poids (LSB : Least Significant Bit) a0 et b0, donne un résultat partiel s0 et une retenue r0. On forme ensuite la somme des deux bits a1 et b1 et de la retenue r0.

Nous obtenons un résultat partiel s1 et une retenue r1. Et ainsi de suite, nous obtenons un résultat sur quatre bits S et une retenue r3.

Considérons la cellule symbolisée sur la figure 2, comptant deux entrées A et B, les deux bits à sommer, et deux sorties D le résultat de la somme et C la retenue.

Ce circuit, qui permettrait d'effectuer l'addition des deux bits de plus bas poids est appelé demi-additionneur (Half-Adder). Ecrivons la table de vérité de celui-ci :

Si nous écrivons ces deux fonctions sous leur forme canonique il vient :

Nous reconnaissons pour la sortie D une fonction OU exclusif, donc :

Ce qui peut être réalisé par le circuit schématisé sur le logigramme de la figure 3.

b) Additionneur

Il faut en fait tenir compte de la retenue des bits de poids inférieurs, un circuit additionneur doit donc comporter trois entrées et deux sorties, comme représenté sur la figure 4.

Ce serait possible en combinant deux demi-additionneurs comme présenté par la figure 5. En pratique pour minimiser le nombre de composants, ou de portes dans un circuit intégré, un tel additionneur est réalisé directement.

Les entrées A et B représentent les bits à additionner et R le report de la retenue de l'addition des bits de poids inférieurs. La sortie S représente le résultat de la somme et C la retenue. La table de vérité de ce circuit est la suivante :

A partir de cette table nous pouvons écrire pour S et C les expressions booléennes suivantes :

Nous pouvons simplifier l'expression de C en utilisant un tableau de Karnaugh :

Nous en déduisons :

C = A B + A R + B R

Le bit de carry est égal à 1 si au moins deux des entrées sont à 1. D'autre part, nous pouvons remarquer qu'intervertir les 0 et les 1 dans la table 2 revient à permuter les lignes 1 et 8, 2 et 7, 3 et 6, 4 et 5. La table de vérité reste globalement invariante par inversion des entrées et des sorties, nous avons donc :

A partir de cette relation, qui peut également être démontrée en appliquant l’algèbre de Boole, nous pouvons écrire :

Ce qui nous permet de réécrire l'expression de S :

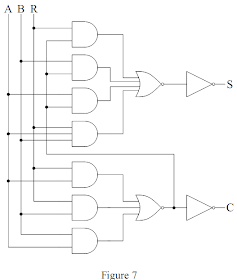

La figure 7 donne un exemple de réalisation d'un additionneur 1 bit basé sur deux portes AOI (AND OR INVERT), c'est-à-dire un ensemble de portes ET suivies d'une porte NON-OU.

c) Addition en parallèle

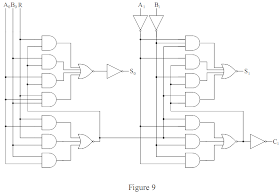

L'addition de nombres comptant plusieurs bits peut se faire en série (bit après bit) ou en parallèle (tous les bits simultanément). La figure 8 montre l'exemple d'un additionneur 4 bits comptant quatre "Full Adders", comparables à celui schématisé figure 7, montés en parallèle ou en cascade. Chaque additionneur FAi est affecté à l'addition des bits de poids i. L'entrée correspondant au report de retenue pour FA0 est imposée à 0 (en logique positive). La retenue finale C indique un dépassement de capacité si elle est égale à 1. Le temps d'établissement du résultat correspondant au temps de propagation des retenues au travers des diverses cellules. Si δt est le temps réponse d'une cellule, la sortie S0 et la retenue R0 sont valables après un retard δt, la sortie S1 et la retenue R1 ne sont correctes qu'après un retard 2 δt, et ainsi de suite. La figure 9 présente un exemple de réalisation logique d'un additionneur de deux mots de 2 bits.

L'addition de nombres comptant plusieurs bits peut se faire en série (bit après bit) ou en parallèle (tous les bits simultanément). La figure 8 montre l'exemple d'un additionneur 4 bits comptant quatre "Full Adders", comparables à celui schématisé figure 7, montés en parallèle ou en cascade. Chaque additionneur FAi est affecté à l'addition des bits de poids i. L'entrée correspondant au report de retenue pour FA0 est imposée à 0 (en logique positive). La retenue finale C indique un dépassement de capacité si elle est égale à 1. Le temps d'établissement du résultat correspondant au temps de propagation des retenues au travers des diverses cellules. Si δt est le temps réponse d'une cellule, la sortie S0 et la retenue R0 sont valables après un retard δt, la sortie S1 et la retenue R1 ne sont correctes qu'après un retard 2 δt, et ainsi de suite. La figure 9 présente un exemple de réalisation logique d'un additionneur de deux mots de 2 bits.

d) Addition séquentielle

Dans un additionneur séquentiel chacun des nombres A et B est représenté par un train d'impulsions (figure 10) synchrones par rapport à un signal d'horloge. L'ordre chronologique d'arrivée des impulsions correspond à l'ordre croissant des poids : le bit le moins significatif se présentant le premier. Ces impulsions sont injectées sur les deux lignes d'entrée d'un additionneur (figure 11). A chaque cycle d'horloge, la retenue provenant des bits de poids inférieurs doit être mémorisée (par exemple, à l'aide d'une bascule D qui sera étudiée dans le chapitre suivant).

Un additionneur parallèle est plus rapide mais nécessite plus de composants.

Dans un additionneur séquentiel chacun des nombres A et B est représenté par un train d'impulsions (figure 10) synchrones par rapport à un signal d'horloge. L'ordre chronologique d'arrivée des impulsions correspond à l'ordre croissant des poids : le bit le moins significatif se présentant le premier. Ces impulsions sont injectées sur les deux lignes d'entrée d'un additionneur (figure 11). A chaque cycle d'horloge, la retenue provenant des bits de poids inférieurs doit être mémorisée (par exemple, à l'aide d'une bascule D qui sera étudiée dans le chapitre suivant).

Un additionneur parallèle est plus rapide mais nécessite plus de composants.

2 - Soustraction

a) Demi-soustracteur

La table de vérité pour un demi-soustracteur (ne tenant pas compte d'une éventuelle retenue provenant des bits de poids inférieurs) est la suivante :

La table de vérité pour un demi-soustracteur (ne tenant pas compte d'une éventuelle retenue provenant des bits de poids inférieurs) est la suivante :

Où D représente le résultat de la soustraction A − B et C la retenue. Nous en déduisons les expressions logiques définissant D et C :

et le schéma correspondant :

Nous pourrions maintenant étudier un soustracteur prenant en compte la retenue. Nous allons plutôt tirer parti de certaines propriétés de la numération binaire pour traiter de la même manière l'addition et la soustraction.

b) Additionneur-soustracteur

Nous savons qu'avec un mot de n bits nous pouvons représenter un entier positif dont la valeur est comprise entre 0 et 2^n − 1. Le complémentaire d'un mot de n bits est obtenu entre prenant le complément de chacun des n bits. Ainsi, si nous sommons un nombre et son complément nous obtenons un mot dont tous les bits sont à 1. C'est-à-dire :

Attention : dans ce paragraphe le signe + représente l'opération addition et non la fonction logique OU. Nous pouvons encore écrire :

Mais sur n bits l'entier 2^n est identique à 0 :

C'est-à-dire qu'il est possible d’écrire un nombre entier négatif comme le "complément à 2" de sa valeur absolue :

Nous reviendrons sur les divers codages des entiers signés plus tard. Nous pouvons utiliser cette propriété pour écrire la soustraction de deux mots de n bits sous la forme suivante :

Ce résultat conduit au schéma de principe présenté sur la figure 13 combinant les fonctions addition et soustraction. Celui-ci est basé sur l'emploi d'un additionneur n bits et d'un multiplexeur à deux lignes d'entrée. Nous étudierons ce type de circuit un peu plus loin dans ce chapitre. Selon le code opération O (0 pour une addition et 1 pour une soustraction) ce multiplexeur permet de sélectionner une des deux entrées, B ou son complémentaire. Le code opération est également injecté sur l'entrée report de retenue de l'additionneur. Pour simplifier le schéma et éviter de représenter n lignes de connexion parallèles, on ne matérialise qu'une seule ligne. Celle-ci est barrée et accompagnée d'une valeur qui indique le nombre réel de connexions.

3 - Comparaison

On rencontre très souvent la nécessité de comparer deux entiers (A = B, A > B ou A < B). Ecrivons la table de vérité correspondant à ces trois fonctions de comparaison de 2 bits. La fonction C doit être égale à 1 si et seulement si A > B, la fonction D si et seulement si A < B et la fonction E si et seulement si A = B. Ce qui nous donne :

Nous en déduisons les expressions logiques de C, D et E :

La figure 14 présente le diagramme d'un bloc logique comparant deux bits A et B.

4 - Contrôle de parité

La parité d'un mot binaire est définie comme la parité de la somme des bits, soit encore :

- parité paire (ou 0) : nombre pair de 1 dans le mot;

- parité impaire (ou 1) : nombre impair de 1 dans le mot.

La fonction OU-exclusif donne la parité d'un sous-ensemble de deux bits. Le contrôle de parité est basé sur la constatation que le mot de n+1 bits formé en adjoignant à un mot de n bits son bit de parité est toujours de parité 0. La figure 15 représente le diagramme logique d'un générateur-contrôleur de parité pour 4 bits. Si l'entrée P' est imposée à 0 ce circuit fonctionne comme générateur de parité : la sortie P représente la parité du mot composé par les bits A, B, C et D.

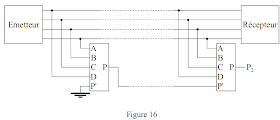

Le contrôle de la parité est utilisé, par exemple, pour augmenter la fiabilité d'un système de transmission ou de stockage de données. La figure 16 montre l'utilisation du circuit précédent en générateur de parité du côté de l'émission et contrôleur de parité du côté de la réception. La sortie P2 doit être à 0 pour chaque mot transmis, sinon cela indique un problème de transmission.

Remarquons cependant que la parité ne permet de détecter qu'un nombre impair de bits en erreur dans un mot. Par ailleurs il ne permet pas corriger les erreurs détectées. Pour ce faire il faut utiliser des codes correcteurs d'erreur qui nécessitent plusieurs bits supplémentaires.

5 - Décodage

Dans un système numérique les instructions, tout comme les nombres, sont transportées sous forme de mots binaires. Par exemple un mot de 4 bits peut permettre d'identifier 16 instructions différentes : l'information est codée. Très souvent l'équivalent d'un commutateur à 16 positions permet de sélectionner l'instruction correspondant à un code. Ce processus est appelé décodage. La fonction de décodage consiste à faire correspondre à un code présent en entrée sur n lignes une seule sortie active parmi les N = 2^n sorties possibles. A titre d'exemple, nous allons étudier le décodage de la représentation DCB des nombres.

a) Représentation DCB (Décimale Codée Binaire)

Le code DCB (ou en anglais BCD : Binary Coded Decimal) transforme les nombres décimaux en remplaçant chacun des chiffres décimaux par 4 chiffres binaires. Cette représentation conserve donc la structure décimale : unités, dizaines, centaines, milliers, etc…

Chaque chiffre est codé sur 4 bits selon le code de la table 6 :

Par exemple le nombre décimal 294 sera codé en DCB : 0010 1001 0100. Ce type de codage permet, par exemple, de faciliter l'affichage en décimal du contenu d'un compteur. Pour ce faire on peut utiliser des tubes de Nixie, contenant 10 cathodes ayant chacune la forme d'un chiffre (fig. 17) ou des afficheurs lumineux à sept segments (fig. 18).

La fonction de chaque décodeur est d'activer une des dix lignes en sortie et une seule en fonction du code présent sur les quatre entrées. Par exemple, si ce code est égal à 5, la 6ème ligne de sortie est mise dans l'état 1 et le chiffre 5 est affiché par le tube de Nixie.

La fonction de chacun des transcodeurs est de positionner à 1 les lignes de sortie correspondant aux segments à allumer selon de code porté par les quatre lignes d'entrée. De manière générale, un transcodeur fait correspondre à un code A en entrée sur n lignes, un code B en sortie sur m lignes.

b) Décodeur DCB-décimal

Nous allons étudier l'exemple d'un décodeur DCB-décimal. La table de vérité de ce décodeur est très simple :

A chacune des lignes de sortie nous pouvons associer un produit prenant en compte chacune des quatre entrées ou leur complément. Ainsi la ligne 5 correspond à :

D'autre part, on souhaite souvent n'activer les lignes de sortie qu'en présence d'un signal de commande global (strobe ou enable). Ce signal S est mis en coïncidence sur chacune des dix portes de sortie. Dans l'exemple suivant, si S est dans l'état 0 le décodeur est bloqué et tous les sorties sont également dans l'état 0.

6 - Multiplexage

Le multiplexage est un dispositif qui permet de transmettre sur une seule ligne des informations en provenance de plusieurs sources ou à destination de plusieurs cibles. La figure 20 en présente une analogie mécanique avec deux commutateurs à plusieurs positions. Choisir une ligne revient à définir l'angle du levier ou une adresse.

Le multiplexage est un dispositif qui permet de transmettre sur une seule ligne des informations en provenance de plusieurs sources ou à destination de plusieurs cibles. La figure 20 en présente une analogie mécanique avec deux commutateurs à plusieurs positions. Choisir une ligne revient à définir l'angle du levier ou une adresse.

a) Démultiplexeur

Un démultiplexeur est un circuit comptant une entrée et N sorties et qui met en relation cette entrée avec une sortie et une seule. Pour pouvoir sélectionner cette sortie il faut également des lignes d'adressage : le code porté par ces lignes identifie la ligne de sortie à utiliser. Ce circuit est très proche d'un décodeur. Considérons un démultiplexeur avec quatre lignes de sortie. Il faut deux lignes d'adresse. Supposons que nous souhaitons également valider les données avec un signal de contrôle E (pour laisser par exemple le temps aux niveaux d'entrée de se stabiliser). Par convention nous choisissons de prendre en compte les données pour E = 0.

De cette table nous déduisons le logigramme suivant :

Il existe sous forme de circuits intégrés des démultiplexeurs avec 2, 4 ou 16 lignes de sortie. Pour constituer des démultiplexeurs d'ordre supérieur on peut être amené à cascader des démultiplexeurs. Par exemple un démultiplexeur avec 32 sorties peut être réalisé avec un "tronc" de 4 sorties et 4 "branches" de 8 sorties :

b) Multiplexeur

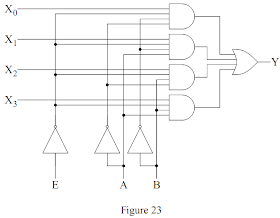

Un multiplexeur, réalise l'opération inverse. Il sélectionne une entrée parmi N et transmet l'information portée par cette ligne à un seul canal de sortie. Considérons un multiplexeur à quatre entrées, donc deux lignes d'adressage, et une ligne de validation. La table de vérité de ce circuit est donnée par la table 9. De cette table nous déduisons une expression logique pour la sortie :

Cette expression correspond au schéma présenté sur la figure 23.

Tout comme pour les démultiplexeurs on peut cascader plusieurs multiplexeurs pour obtenir un multiplexeur d'ordre supérieur. La figure 24 montre comment un multiplexeur à 32 entrées peut être réalisé à partir de quatre multiplexeurs à 8 entrées et d'un multiplexeur à 4 entrées.

c) Conversion parallèle-série

Considérons un mot de n bits (par exemple 4) présent en parallèle sur les entrées d'un multiplexeur :

Considérons un mot de n bits (par exemple 4) présent en parallèle sur les entrées d'un multiplexeur :

Supposons que les lignes d'adresse A et B soient connectées aux sorties d'un compteur de période T, nous aurons en fonction du temps :

Les bits X0, X1, X2 et X3 se retrouvent en série dans le temps sur la sortie Y du multiplexeur.

d) Réalisation d’une fonction logique

Un multiplexeur peut être utilisé pour réaliser une fonction logique. Il permet en effet une transcription directe de la table de vérité. Considérons par exemple la fonction de quatre variables logiques F(x, y, z, t) définie par la table suivante :

Il est possible d’utiliser un multiplexeur à 16 entrées. Il suffit de connecter les variables logiques x, y, z et t sur les entrées d’adresse et de mettre chacune des entrées Xk à 0 ou 1 selon la table de vérité.

7 - Encodage

Nous venons d'étudier le principe du décodage, passons à l'opération inverse ou encodage.

Un encodeur est un système qui comporte N lignes d'entrée et n lignes de sortie. Lorsqu’une des lignes d'entrée est activée l'encodeur fournit en sortie un mot de n bits correspondant au codage de l'information identifiée par la ligne activée.

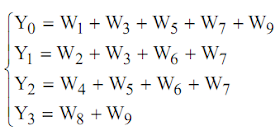

Considérons un encodeur transformant un nombre décimal en son équivalent en code DCB. Il comportera donc 10 entrées (0 à 9) et 4 sorties. Nous pouvons par exemple imaginer que chacune des dix lignes d'entrée peut être reliée à une touche d'un clavier. La table 12 correspond à la table de vérité de cet encodeur. A partir de cette table nous pouvons écrire les expressions logiques définissant les sorties à partir des entrées.

En effet Y0 est égal à 1 quand la ligne W1 est dans l'état 1, ou la ligne W3, ou la ligne W5, ou la ligne W7, ou la ligne W9. La ligne Y0 est nulle dans tous les autres cas. Il est possible de réaliser ces fonctions OU avec des diodes selon le montage de la figure suivante :

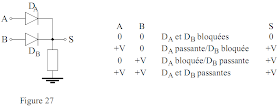

En effet considérons le circuit de la figure 27 :

Si nous traduisons la signification logique des niveaux haut et bas en logique positive, au circuit de la figure 27 correspond la table de vérité 13. La fonction réalisée est donc un OU inclusif.

La figure 26 représente un exemple de réalisation d’un encodeur DCB réalisé avec des diodes. Le bon fonctionnement de ce codeur suppose qu'une seule ligne d'entrée peut être dans l'état 1.

Par contre, si plusieurs entrées sont actives simultanément le résultat pourra ne pas avoir de signification. Par exemple, si les deux lignes W7 et W8 sont dans l'état 1 (frappe simultanée des deux touches), il en sera de même pour les quatre sorties. Pour éviter ce problème on utilise un encodeur prioritaire. Pour ce type de circuit si plusieurs lignes d'entrée sont actives simultanément le résultat correspondant à une seule parmi celles-ci est affiché en sortie. La règle peut être, par exemple, de mettre en sortie le code correspondant à la ligne d'entrée d'indice le plus élevé. Par exemple, si W7 et W8 sont dans l'état 1 l'encodeur prioritaire donne en sortie le code correspondant à W8. La table de vérité correspondant à ce choix est donnée par la table 14. Chaque croix indique que le code en sortie doit être indépendant de l'état de l'entrée concernée.

Alors que les expressions logiques définissant les lignes de sortie Yi ne dépendaient que des 1 dans la table 11, il faut ici tenir compte des 0. Par exemple pour Y0 nous avons :

Nous pouvons mettre le complémentaire de W9 en facteur dans les quatre premiers termes, puis en utilisant l'identité :

il vient, après factorisation du complément de W8 :

Soit encore :

Soit en réorganisant l'ordre des termes :

Pour la ligne Y1 nous avons :

Soit en factorisant :

En utilisant toujours la même identité nous pouvons simplifier cette expression, il vient en réordonnant les termes :

Pour Y2 nous devons écrire :

Soit encore :

En utilisant toujours la même identité il vient :

Enfin pour Y3 nous avons :

Aucun commentaire:

Enregistrer un commentaire