Exercice Corrigé Architecture des ordinateurs TP Architecture des ordinateurs HardWare

1) Architecture générale

Question 1 : Complétez les schéma de la machine de von Neuman suivant :

Question 1 : Complétez les schéma de la machine de von Neuman suivant :

Question 2 : Complétez le schéma du PC suivant :

Question 3 : Identifiez les composants sur la carte mère suivante :

2 ) Bus

Question 4 : Bus mémoire. Calculez les taux de transferts suivants :

Question 5 : Bus périphérique. Calculez les taux de transferts suivants :

3) Processeur

Question 6 : Sachant que le bus d’adresse du processeur est de 16 bits avec un alignement à l’octet, quelle est la taille de l’espace mémoire maximum que celui-ci peut adresser ? Quels solutions existent pour adresser une plus grande zone mémoire ?

Question 7 : Où sont effectués les calculs ?

Question 8 : A quoi servent les registres suivants du processeur :

i. PC/IP (ou CO/PI)

ii. IR (ou RI)

iii. SP (ou PP)

iv. Accumulateur

Question 9 : Quel tâche réalise le séquenceur dans un processeur ? l'ordonnanceur ?

4 ) Mémoires

Question 10 : Quelles sont les principales différences entre la DRAM et la SRAM ? Où utilise-t-on de la DRAM ? De la SRAM ?

Question 11 : Quelles sont les principales différences entre la RAM et la ROM ? Où utilise-t-on de la ROM ?

Question 12 : Qu’est-ce que le shadowing ?

Question 13 : Classez les mémoires suivantes par taille, par rapidité : RAM, registres, disques durs, cache L1, cache L2, cd-rom.

Question 14 : Quels sont les propriétés des disques RAIDs ? Comment les obtient-on ?

5 ) Mémoire cache

Question 15 : Pourquoi utilise-t-on des mémoires caches ?

Soit une mémoire cache de niveau L1 ayant les caractéristiques suivantes :

Question 13 : Classez les mémoires suivantes par taille, par rapidité : RAM, registres, disques durs, cache L1, cache L2, cd-rom.

Question 14 : Quels sont les propriétés des disques RAIDs ? Comment les obtient-on ?

5 ) Mémoire cache

Question 15 : Pourquoi utilise-t-on des mémoires caches ?

Soit une mémoire cache de niveau L1 ayant les caractéristiques suivantes :

- 32 mots par lignes (mots de 2 octets)

- Taille de 32ko

- L1 et L2 sont inclusifs

- 4-associatifs. Remplacement LRU.

- Association par poids faible

- Taille de bus d’adresse : 32bits

Question 16 : Combien y a-t-il de lignes dans cette mémoire cache ?

Question 17 : Combien y-a-t-il de blocs associatifs dans cette mémoire cache ?

Question 18 : Si la mémoire cache de niveau L2 a une taille de 2 Mo, combien y a-t-il de blocs de la mémoire cache L2 par bloc de la mémoire cache L1 ?

Question 19 : Si la mémoire fait 1Go, combien d’adresses correspondront à un bloc du cache L1 ?

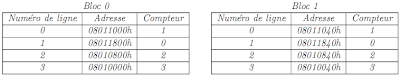

Question 20 : Dans quelles blocs du cache peut-on trouver les blocs suivants :

Question 21 : Si un bloc n’est pas présent en cache L1, combien de lignes de L1 aura-t-on parcouru ?

Question 22 : Quelle est la probabilité de trouver un bloc quelconque présent dans L2 dans la cache L1 ?

- Si L1 et L2 sont des caches inclusives.

- Si L1 et L2 sont des caches exclusives.

Question 23 : Dans cet exercice, on considère qu’il n’y a que 64 blocs de cache L1.

Les lignes d’adresses suivantes sont lues dans l’ordre : 08012000h, 08012040h, 08020080h, 080220C0h,

08012080h, 080120C0h, 080220C0h, 080520C0h, 08022080h, 08021080h, 08012800h, 08012840h, 08012880h, 080128C0h. Donnez l’état du cache après ces lectures.

----------------------------------------------------------------------------------------------------

----------------------------------------------------------------------------------------------------

Je veux télécharger

RépondreSupprimerMe too

RépondreSupprimerRéponse de la question 13

RépondreSupprimer