Logique séquentielle : asynchrone et synchrone - Les bascules - Compteurs - Registres

Logique séquentielle

Note :

!Q

vaut :

1 - Logique séquentielle asynchrone et synchrone

Dans le chapitre précédent portant sur la logique combinatoire nous avons fait abstraction du temps : les signaux de sortie ne dépendaient que des états des variables d'entrée. Pour les circuits de logique séquentielle nous devons tenir compte de l'état du système. Ainsi les sorties dépendent des entrées mais également de l'état du système. Celui-ci dépend aussi des entrées. Si nous notons Q l'état d'un système séquentiel, X ses entrées et Y ses sorties, nous avons de manière générale :

La logique séquentielle permet de réaliser des circuits dont le comportement est variable avec le temps. L'état d'un système constitue une mémoire du passé.

Lorsque les changements d'état des divers composants d'un circuit séquentiel se produisent à des instants qui dépendent des temps de réponse des autres composants et des temps de propagation des signaux on parle de logique séquentielle asynchrone. Cependant les retards peuvent ne pas être identiques pour toutes les variables binaires et conduire à certains aléas. Ceux-ci peuvent être évités en synchronisant la séquence des diverses opérations logiques sur les signaux périodiques provenant d'une horloge. La logique séquentielle est alors dite synchrone : tous les changements d'état sont synchronisés sur un signal de contrôle.

Nous commençons notre étude par celle des bascules, éléments de base des circuits séquentiels. Puis nous étudierons les registres et les compteurs.

2 - Les bascules

Une bascule (flip-flop) a pour rôle de mémoriser une information élémentaire. C'est une mémoire à 1 bit. Une bascule possède deux sorties complémentaires Q et !Q. La mémorisation fait appel à un verrou (latch) ou système de blocage, dont le principe de rétro-action peut être représenté de la façon suivante :

Lorsque les changements d'état des divers composants d'un circuit séquentiel se produisent à des instants qui dépendent des temps de réponse des autres composants et des temps de propagation des signaux on parle de logique séquentielle asynchrone. Cependant les retards peuvent ne pas être identiques pour toutes les variables binaires et conduire à certains aléas. Ceux-ci peuvent être évités en synchronisant la séquence des diverses opérations logiques sur les signaux périodiques provenant d'une horloge. La logique séquentielle est alors dite synchrone : tous les changements d'état sont synchronisés sur un signal de contrôle.

Nous commençons notre étude par celle des bascules, éléments de base des circuits séquentiels. Puis nous étudierons les registres et les compteurs.

2 - Les bascules

Une bascule (flip-flop) a pour rôle de mémoriser une information élémentaire. C'est une mémoire à 1 bit. Une bascule possède deux sorties complémentaires Q et !Q. La mémorisation fait appel à un verrou (latch) ou système de blocage, dont le principe de rétro-action peut être représenté de la façon suivante :

Nous pouvons vérifier :

Une bascule ne peut donc être que dans deux états : "1"

Les interconnexions du verrou interdisent les deux autres combinaisons :

Ce type de circuit, qui n'a que deux états stables possibles, est encore appelé circuit bistable.

Un verrou permet de conserver un état, il nous faut maintenant savoir comment charger cet état.

a) Les bascules R-S

Les verrous les plus fréquemment rencontrés sont réalisés avec deux portes NOR ou NAND. Considérons dans un premier temps le circuit suivant :

La table 1 donne la table de vérité correspondante. Si on applique S = 1 et R = 0 ou S = 0 et R = 1 on impose l'état de la sortie Q respectivement à 1 ou à 0, la sortie !Q prenant la valeur complémentaire. Cet état se maintient lorsque les deux entrées retournent à 0. La configuration S = R = 1 est à proscrire car ici elle conduit à Q = !Q = 0 , ce qui est inconsistant logiquement avec notre définition. Mais surtout, lorsque R et S reviennent à 0, l'état Q = !Q étant incompatible avec les interconnexions, l'une de ces deux sorties va reprendre l'état 1, mais il est impossible de prédire laquelle : la configuration S = R = 1 conduit à une indétermination de l'état des sorties et est donc inutilisable. La représentation d'une bascule RS est donnée sur la figure 4.

Considérons maintenant la bascule réalisée avec des portes NON-ET.

Il lui correspond la table de vérité suivante :

L'utilisation des deux inverseurs sur les lignes d'entrée nous permet de retrouver une table de vérité comparable à celle de la bascule RS précédente.

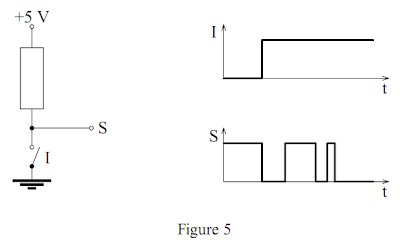

b) Dispositif anti-rebond

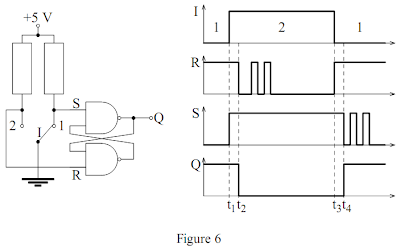

On est souvent amené à commander un état physique à l'aide d'un bouton poussoir ou d'un inverseur (par exemple les touches d'un clavier). Cependant lorsqu'on ferme un interrupteur le contact n'est pas franc instantanément et on peut observer une série de rebonds du signal avant d'obtenir la position fermée (fig. 5). Pour éviter ce défaut on réalise un montage équivalent à celui présenté sur la figure 6 faisant appel à un inverseur et une bascule.

Supposons l'interrupteur initialement dans la position 1 comme indiqué par la figure 6 :

l'entrée S est à la masse donc, en logique positive, dans l'état logique "0" et l'entrée R sous tension c'est-à-dire dans l'état logique "1". La sortie Q se trouve donc dans l'état "1". A l'instant t1 nous basculons l'interrupteur de la position 1 à la position 2. Dès que le contact est ouvert en 1 l'entrée S se trouve sous tension et passe dans l'état logique "1". Par contre le contact en 2 peut s'établir avec un léger retard dû au mouvement du contacteur et ne pas être immédiatement franc. L'entrée R passe dans l'état "0" à t2, quelques rebonds peuvent suivre. A t2 lorsque les entrées se trouvent dans la configuration S = 1 et R = 0 la sortie Q passe dans l'état "0". Par contre dans la configuration S = 1 et R = 1, c'est-à-dire entre t1 et t2 et pendant les rebonds, les sorties restent inchangées : les rebonds ne sont pas visibles sur la sortie Q. Le fonctionnement est symétrique lors du passage de la position 2 à 1.

3 - Bascule R.S.T ou R.S.Clock

La bascule R.S.T. est une bascule pour laquelle les entrées S et R ne sont prises en compte qu'en coïncidence avec un signal de commande. Ce signal peut être fourni par une horloge, nous avons alors une bascule synchrone. Ce circuit peut être réalisé de la façon suivante et sa représentation est donnée sur la figure 8.

l'entrée S est à la masse donc, en logique positive, dans l'état logique "0" et l'entrée R sous tension c'est-à-dire dans l'état logique "1". La sortie Q se trouve donc dans l'état "1". A l'instant t1 nous basculons l'interrupteur de la position 1 à la position 2. Dès que le contact est ouvert en 1 l'entrée S se trouve sous tension et passe dans l'état logique "1". Par contre le contact en 2 peut s'établir avec un léger retard dû au mouvement du contacteur et ne pas être immédiatement franc. L'entrée R passe dans l'état "0" à t2, quelques rebonds peuvent suivre. A t2 lorsque les entrées se trouvent dans la configuration S = 1 et R = 0 la sortie Q passe dans l'état "0". Par contre dans la configuration S = 1 et R = 1, c'est-à-dire entre t1 et t2 et pendant les rebonds, les sorties restent inchangées : les rebonds ne sont pas visibles sur la sortie Q. Le fonctionnement est symétrique lors du passage de la position 2 à 1.

3 - Bascule R.S.T ou R.S.Clock

La bascule R.S.T. est une bascule pour laquelle les entrées S et R ne sont prises en compte qu'en coïncidence avec un signal de commande. Ce signal peut être fourni par une horloge, nous avons alors une bascule synchrone. Ce circuit peut être réalisé de la façon suivante et sa représentation est donnée sur la figure 8.

Lorsque le signal de commande, noté ici Clk, est à 1 la bascule fonctionne comme indiqué précédemment et les sorties suivent les variations des entrées S et R. Par contre, lorsque le signal de commande est à 0, la bascule est bloquée : Q est indépendant des éventuels changements de S et R. L'état mémorisé correspond au dernier état avant le passage de la ligne de commande de 1 à 0.

Dans un système synchrone le signal de commande est fourni par une horloge (clock).

Celui-ci est constitué par une succession périodique d'impulsions de largeur tp, supposée petite devant la période T. L'état de chacune des sorties restera donc bloqué pendant les intervalles séparant deux impulsions. Nous notons Qn la valeur de la sortie Q pendant le nième intervalle précédant la nième impulsion et Qn+1 la valeur correspondante dans l'intervalle suivant la nième impulsion (fig 9).

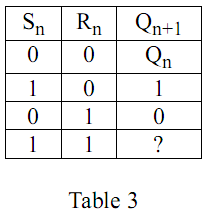

Considérons l'instant t = nT + ε, où Clk = 1. Si S = R = 0, la sortie Q ne change pas donc Qn+1 = Qn. Si S = 1 et R = 0 alors la sortie Q est forcée à 1. Si R = 1 et S = 0 alors la sortie Q est mise à 0. Si S = R = 1 alors les deux sorties Q et !Q sont toutes les deux à 1. Cet état est instable et ne persiste pas lorsque le signal de commande revient à 0. L'état final sera indéterminé, dépendant des vitesses relatives des portes. Cette situation ne doit pas être autorisée. L'état Q reste ensuite figé jusqu'à (n+1)T. Si nous notons Sn et Rn les valeurs de S et R juste avant l'instant t = nT nous pouvons écrire la table de vérité :

4 - Bascules J-K, D et T

a) Bascule J-K

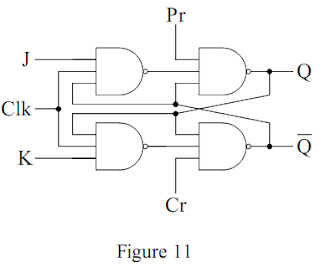

La bascule J-K permet de lever l'ambiguïté qui existe dans la table 3. Ceci peut être obtenu en asservissant les entrées R et S aux sorties Q et !Q selon le schéma logique indiqué sur la figure 10.

Nous avons alors pour les signaux R et S :

Ce qui nous permet de construire la table de vérité de la bascule J-K.

Nous constatons que nous ne rencontrons jamais la combinaison R = S = 1. Cette table peut se résumer sous la forme suivante :

La figure 11 explicite le diagramme logique d'une bascule J-K. Le rôle des entrées Pr et Cr sera étudié dans le prochain paragraphe.

A partir de la table 5 nous pouvons construire la table de transition de la bascule J-K. La table 6 donne les états dans lesquels doivent se trouver les entrées J et K pour obtenir chacune des quatre transitions possibles de la sortie Q. Une croix indique que l'état de l'entrée considérée est indifférent : 0 ou 1. Par exemple, pour obtenir la transition 0 → 1 de la sortie Q il faut que l'entrée J soit dans l'état 1, quelque soit l'état de l'entrée K. En effet, nous pouvons avoir J = K = 1 qui inverse l'état de la bascule ou J = 1 et K = 0 qui charge 1 dans la bascule.

Comme les deux entrées ne sont jamais spécifiées simultanément il est possible de choisir pour simplifier l'égalité des deux entrées :

J = K

On utilise parfois l'expression logique donnant Qn+1 en fonction de Jn, Kn et Qn. Pour cela nous pouvons par exemple construire le tableau de Karnaugh à partir de la table de vérité (table 4) de la bascule J-K :

D'où nous tirons l'équation caractéristique qui exprime l'état futur en fonction de l'état présent et des entrées :

b) Preset et Clear

Les entrées asynchrones (car à utiliser en absence de signal d'horloge, lorsque Clk = 0) Pr (Preset) et Cr (Clear) permettent d'assigner l'état initial de la bascule, par exemple juste après la mise sous tension pour éviter tout aléa. En fonctionnement normal ces deux entrées doivent être maintenues à 1. Lorsque le signal d'horloge est à 0 nous avons la table de vérité suivante :

La figure 12 donne la représentation symbolique d'une bascule J-K avec les entrées Preset et Clear.

c) Bascule J-K Maître-Esclave

Jusqu'à présent nous avons construit les tables de vérité à partir de la logique combinatoire qui suppose que les entrées sont indépendantes des sorties. Or dans la bascule J-K nous avons introduit des connexions d'asservissement entre les entrées et les sorties. Ainsi supposons qu'avant le signal d'horloge nous avons J = K = 1 et Q = 0 (notations de la figure 11). Lorsque le signal d'horloge passe à 1 la sortie Q devient 1. Ce changement intervient après un intervalle de temps ∆t. Nous avons alors J = K = Q = 1. D'après la table 4 nous voyons que la sortie Q doit alors revenir à 0. Ainsi la sortie Q va osciller entre 0 et 1 pendant toute la durée du signal d'horloge rendant le résultat ambigu.

Pour éviter ce problème on monte deux bascules R-S en cascade (fig. 13) en asservissant les entrées de la première (Maître) aux sorties de la seconde (Esclave). D'autre part, le signal d'horloge parvenant à l'esclave est inversé. Supposons Pr = Cr = 1. Pendant la nième impulsion le signal d'horloge est haut pour le maître et bas pour l'esclave. L'état Qn est donc invariant pendant la durée tp de l'impulsion. Le problème précédent est donc résolu et l'état de la sortie de la bascule maître QM est donné par la table 5. Ensuite lorsque le signal d'horloge passe à 0 pour le maître celui-ci est bloqué alors que l'esclave est libéré. Nous avons alors :

L'état de la bascule maître est transféré à la bascule esclave lors de la transition 1 → 0 (front descendant) du signal d'horloge. Les changements d’état éventuels des sorties Q et !Q interviennent donc sur le front descendant du signal de commande Clk. Les entrées J et K qui définissent le nouvel état de ces sorties sont prises en compte lorsque le signal Clk est à 1.

Les entrées J et J doivent rester stables lorsque le signal Clk est haut. Dans la pratique elles doivent être stabilisées avant le front montant (temps de stabilisation) et le rester un peu après le front descendant (temps de maintien).

d) Déclenchement sur front montant ou descendant du signal d’horloge

Le problème de l’oscillation de la bascule J-K lorsque le signal Clk est haut, réglé par les deux étages de la bascule maître-esclave, peut également être éliminé par l’utilisation d’un détecteur de front. Un tel circuit produit en coïncidence avec le front montant ou le front descendant du signal Clk une impulsion de largeur juste suffisante pour permettre un basculement d’état. Les figures suivantes illustrent le principe d’un détecteur de front montant (fig. 15) et d’un détecteur de front descendant (fig. 16). Une fois n’est pas coutume dans ce cours, nous tenons compte d’un retard induit par l’inverseur.

Il suffit d’insérer un détecteur de front avant les deux premières portes NON-ET (figure suivante) pour obtenir une bascule J-K déclenchée par le front montant ou le front descendant du signal d’horloge.

La figure 18 présente les symboles d’une bascule déclenchée par le front montant et d’une bascule déclenchée par le front descendant du signal de commande.

Une bascule D (Delay) est obtenue à partir d'une bascule J-K en envoyant simultanément une donnée sur l'entrée J et son inverse sur l'entrée K (fig. 19).

A partir de la table 5 nous pouvons écrire :

Ce qui peut se résumer par Qn+1 = Dn. Ainsi l'état de la bascule Q pendant l'intervalle n+1 est égal à la valeur de l'entrée D pendant l'intervalle n. Une bascule D agit comme une unité à retard pour laquelle la sortie suit l'entrée avec un cycle de retard. Sa représentation symbolique est donnée par la figure 20.

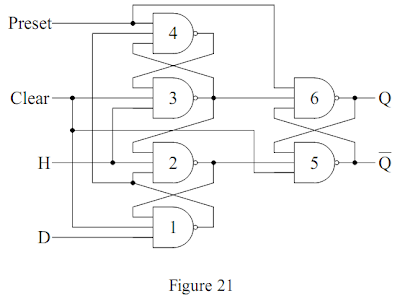

f) Bascule D à commande sur front montant

Nous nous intéressons ici à une seconde technique pour réaliser une bascule D pour laquelle la valeur de l'entrée D présente au moment de la transition 0 → 1 du signal d'horloge est chargée dans la bascule. Ensuite, que H soit égal à 1 ou à 0, la bascule est isolée de l'extérieur jusqu'au prochain front montant du signal H. L'entrée doit être stabilisée un peu avant la transition de H et conserver cette valeur un certain temps après.

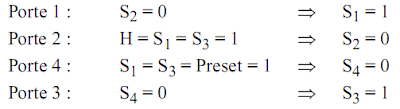

Considérons le circuit schématisé sur la figure 21. Notons S1, S2, S3 et S4 les sorties des portes NAND numérotées respectivement 1, 2, 3 et 4. En fonctionnement normal nous devons avoir Clear = 1 pour ne pas bloquer les portes 1, 3 et 5 et Preset = 1 pour ne pas bloquer les portes 4 et 6. Pour H = 0 nous avons S2 = S3 = 1. Considérons maintenant le passage de H à 1.

1er cas : D = 1

2ème cas : D = 0

Dans les deux cas nous vérifions que Q = D. Maintenant considérons une transition de D alors que le signal H est encore à 1.

1er cas : D = 1 → 0 (juste avant cette transition nous avons : S1 = S3 = 0, S2 = S4 = 1)

2ème cas : D = 0 → 1 (juste avant cette transition nous avons : S1 = S3 = 1, S2 = S4 = 0)

Dans les deux cas la sortie Q reste inchangée. Etudions maintenant les opérations de Remise à Zéro et Remise à Un :

Preset = 0 et Clear = 1 :

Preset = 1 et Clear = 0 :

g) Bascule T

Dans la table 5 nous constatons que si J = K = 1 alors Qn+1 = !Qn . L'état de la sortie est inversé à chaque cycle d'horloge. Une bascule T (Trigger) est obtenue à partir d'une bascule J-K en injectant le même état dans les entrées J et K (fig. 22). Sa table de vérité est donnée dans la table 7 et sa représentation par la figure 23.

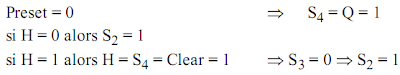

5 - Registre de mémorisation

Un registre permet la mémorisation de n bits. Il est donc constitué de n bascules, mémorisant chacune un bit. L'information est emmagasinée sur un signal de commande et ensuite conservée et disponible en lecture. La figure 24 donne un exemple de registre 4 bits réalisé avec quatre bascules D.

En synchronisme avec le signal d'écriture W le registre mémorise les données présentent sur les entrées E0, E1, E2 et E3. Elles sont conservées jusqu'au prochain signal de commande W. Dans cet exemple les états mémorisés peuvent être lus sur les sorties Q0, Q1, Q2 et Q3 en coïncidence avec un signal de validation R. Lorsque ces sorties sont connectées à un bus, les portes ET en coïncidence avec ce signal de lecture sont remplacées par des portes à trois états.

6 - Registre à décalage

Dans un registre à décalage les bascules sont interconnectées de façon à ce que l'état logique de la bascule de rang i puisse être transmis à la bascule de rang i+1 (ou i-1) quand un signal d'horloge est appliqué à l'ensemble des bascules. L'information peut être chargée de deux manières dans ce type de registre.

- Entrée parallèle : comme dans le cas d'un registre de mémorisation. En général une porte d'inhibition est nécessaire pour éviter tout risque de décalage pendant le chargement parallèle.

- Entrée série : l'information est présentée séquentiellement bit après bit à l'entrée de la première bascule. A chaque signal d'horloge un nouveau bit est introduit pendant que ceux déjà mémorisés sont décalés d'un niveau dans le registre. La figure 25 schématise le chargement d'un registre 4 bits en quatre coups d'horloge.

De même l'information peut être lue en série ou en parallèle. D'autre part, certains registres peuvent être capables de décaler à gauche et à droite. Un registre à décalage universel serait donc constitué des entrées, des sorties et des commandes suivantes :

Généralement on utilise des bascules du type maître-esclave D ou R-S.

a) Entrée série - Sortie parallèle

La figure suivante donne un exemple de registre de 4 bits à entrée série et sortie parallèle réalisé avec des bascules D.

Ce type de registre permet de transformer un codage temporel (succession des bits dans le temps) en un codage spatial (information stockée en mémoire statique).

La sortie série peut également être utilisée. L'intérêt d'utilisation d'un registre à décalage en chargement et lecture série réside dans la possibilité d'avoir des fréquences d'horloge différentes au chargement et à la lecture. Le registre constitue alors un tampon.

b) Entrée parallèle - sortie série

La figure 28 présente un exemple de registre à décalage à entrée parallèle ou série et sortie série. Si X = 1 l'entrée parallèle est inhibée et l'entrée série est validée. Si X = 0 l'entrée série est bloquée par contre le chargement par l'entrée parallèle est autorisé.

Un registre à décalage à entrée parallèle et sortie série transforme un codage spatial en codage temporel.

c) Entrée parallèle - Sortie parallèle

La figure 29 présente un exemple de registre à décalage avec entrées série et parallèle et sorties série et parallèle réalisé avec des bascules de type D.

La commande permet de sélectionner le mode de chargement et d'inhiber le signal d'horloge en cas de chargement parallèle. Si X = 0 nous avons Pr = Cr = 1, ce qui garantit le fonctionnement normal des bascules. Si X = 1 alors selon l'état de chacune des entrées nous avons :

d) Registre à décalage à droite et à gauche

La figure 30 présente un exemple de registre à décalage universel de 4 bits. Les diverses possibilités sont sélectionnées par les lignes commande S0 et S1. Considérons la ligne transportant le signal d'horloge aux bascules, elle est gouvernée par l'expression logique :

La figure 30 présente un exemple de registre à décalage universel de 4 bits. Les diverses possibilités sont sélectionnées par les lignes commande S0 et S1. Considérons la ligne transportant le signal d'horloge aux bascules, elle est gouvernée par l'expression logique :

Le signal d'horloge sera donc inhibé si S0 = S1 = 0.

Pour sélectionner le chargement parallèle (entrées A, B, C et D) il faut :

C'est-à-dire S0 = S1 = 1. Le chargement se fera sur un signal d'horloge.

Pour sélectionner le décalage à droite (entrée E1, sortie QD) il nous faut S0 = 1 et S1 = 0 et pour le décalage à gauche (entrée E0, sortie QA) S0 = 0 et S1 = 1. Ce qui est résumé dans le tableau 8.

Un registre à décalage à droite et à gauche permet d'effectuer des multiplications et des divisions entières par des puissances de 2. En effet une multiplication par 2 est équivalente à un décalage vers la gauche et une division par 2 à un décalage vers la droite. Une multiplication par 2n sera obtenue par n décalages à gauche et une division par 2n par n décalages à droite.

7 - Compteurs

Un compteur est un ensemble de n bascules interconnectées par des portes logiques. Ils peuvent donc mémoriser des mots de n bits. Au rythme d'une horloge ils peuvent décrire une séquence déterminée c'est-à-dire occuper une suite d'états binaires. Il ne peut y avoir au maximum que 2^n combinaisons. Ces états restent stables et accessibles entre les impulsions d'horloge. Le nombre total N des combinaisons successives est appelé le modulo du compteur. On a N ≤ 2^n. Si N < 2^n un certain nombre d'états ne sont jamais utilisés.

Les compteurs binaires peuvent être classés en deux catégories :

- les compteurs asynchrones;

- les compteurs synchrones.

De plus on distingue les compteurs réversibles ou compteurs-décompteurs.

8 - Compteurs asynchrones

Un compteur asynchrone est constitué de n bascules J-K fonctionnant en mode T. Le signal d'horloge n'est reçu que par le premier étage (bascule LSB : Least Significant Bit). Pour chacune des autres bascules le signal d'horloge est fourni par une sortie de la bascule de rang immédiatement inférieur.

Considérons par exemple (fig. 31) un compteur modulo 8 suivant le code binaire pur constitué de trois bascules J-K maîtres-esclaves. Supposons les trois bascules à zéro à l'instant t = 0. Nous avons vu que pour une bascule maître-esclave la sortie change d'état juste après le passage du signal d'horloge de l'état 1 à l'état 0 (front descendant). L'évolution temporelle des trois sorties Q0, Q1 et Q2 par rapport aux impulsions d'horloge est représentée sur la figure 32. La sortie Q0 bascule sur chaque front descendant du signal d'horloge. La sortie Q1 change d'état à chaque transition 1 → 0 de la sortie Q0. De même le basculement de la sortie Q2 est déclenché par une transition 1 → 0 de la sortie Q1.

A partir de ce chronogramme nous pouvons écrire la liste des états successifs des trois sorties :

Nous avons réalisé un compteur s'incrémentant d'une unité à chaque top d'horloge, avec un cycle de huit valeurs de 0 à 7 (modulo 8).

Nous constatons que les sorties Q0, Q1 et Q2 fournissent des signaux périodiques de fréquences respectivement 2, 4 et 8 fois plus faibles. La division de fréquence est une des applications des compteurs.

a) Compteur-décompteur asynchrone

Nous obtenons un compteur en déclenchant chaque bascule lorsque celle de rang immédiatement inférieur passe de l'état 1 à 0. Pour réaliser un décompteur il faut que le changement d'état d'une bascule intervienne lorsque la bascule de rang immédiatement inférieur passe de l'état 0 à 1. Pour cela il suffit d'utiliser la sortie !Q de chaque bascule pour déclencher la suivante.

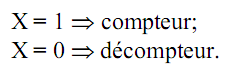

On réalise un compteur-décompteur en utilisant un multiplexeur 2 entrées - 1 sortie entre chaque étage pour sélectionner la sortie à utiliser. Pour l'exemple présenté sur la figure 33, selon l'état de la ligne de commande X nous pouvons sélectionner le mode de comptage :

b) Remise à Zéro et chargement d'un compteur

La figure 34 présente un exemple de montage permettant de remettre à zéro un compteur ou de le charger avec une valeur déterminée. Pour cela on utilise les entrées asynchrones des bascules. En fonctionnement normal du compteur nous devons avoir : DS = R = 1. Nous avons alors : J = K = Pr = Cr = 1 sur chaque bascule du compteur.

Pour RAZ : R = 0

Chargement : (DS = 0, R = 1)

Dans ces deux cas nous obtenons Q = D. Nous sommes donc capable de charger chaque bit du compteur avec une valeur donnée à présenter sur l'entrée D, donc d'initialiser le compteur.

c) Compteur à cycle incomplet

On peut souhaiter compter jusqu'à un nombre N qui ne soit pas une puissance de 2, par exemple 10 (système décimal). Pour cela on utilise un compteur de n bascules, tel que 2^n > N. On lui ajoute un asservissement de l'entrée Clear pour remettre le compteur à zéro tous les N coups.

Considérons par exemple un compteur modulo 10. Nous voulons que l'entrée Clear soit à 0 lorsque le compteur atteint 1010 = 10102. Pour cela nous pouvons écrire l'expression logique :

En fait dans ce cas particulier nous pouvons simplifier cette relation logique en ne tenant compte de ce que des sorties à 1 dans l'expression binaire de N. En effet il ne peut y avoir ambiguïté : toute combinaison contenant les mêmes sorties à 1 et au moins une autre à 1 correspond à un nombre plus grand que N et ne peut être rencontrée dans la séquence décrite par le compteur.

Pour un compteur modulo 10 nous pouvons donc utiliser :

ce qui nous conduit au schéma suivant :

d) Inconvénients des compteurs asynchrones

Comme chaque bascule a un temps de réponse le signal d'horloge ne parvient pas simultanément sur toutes les bascules. Ceci a pour conséquence de provoquer des états transitoires qui peuvent être indésirables. Supposons un temps de réponse tr identique pour toutes les bascules. Considérons la chronologie du passage d'un compteur asynchrone 4 bits de 0111 à 1000. Celle-ci est présentée sur la figure 36. Nous constatons que le compteur passe par les états transitoires 0110, 0100 et 0000 qui sont faux. Ceci est un inconvénient rédhibitoire chaque fois que la sortie du compteur est exploitée par des organes rapides.

9 - Compteurs synchrones

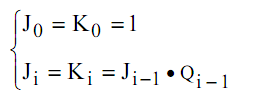

Dans un compteur synchrone toutes les bascules reçoivent en parallèle le même signal d'horloge. Pour faire décrire au compteur une séquence déterminée il faut à chaque impulsion d'horloge définir les entrées synchrones J et K. Pour cela on utilise la table de transition de la bascule J-K (table 6). Nous avons déjà remarqué que cette table peut se simplifier. En effet, pour chacune des quatre transitions possibles une seule des entrées J ou K est définie. Rien ne nous interdit donc de les mettre dans le même état, c'est-à-dire J = K, comme dans une bascule T.

Prenons l'exemple d'un compteur synchrone 3 bits fonctionnant selon le code binaire pur. Nous pouvons dresser un tableau précisant les valeurs des entrées J et K permettant d'obtenir chaque transition (passage d'une ligne à la suivante). Pour qu'une bascule change d'état il faut que ses deux entrées soient à 1.

Chaque ligne de cette table correspond à une même tranche de temps. Il est assez facile d'en déduire les expressions logiques reliant les entrées aux sorties :

De manière générale nous pouvons vérifier que les équations de commutation satisfont les relations de récurrence suivantes :

ou encore :

Procédons de même pour réaliser un décompteur, nous écrivons la table des transitions recherchées :

Nous en déduisons l'expression logique des entrées d'un décompteur :

Nous constatons que les équations de commutation sont identiques en utilisant cette fois les sorties complémentaires !Q.

Aux deux manières d'exprimer les relations de récurrence des équations de commutation correspondent deux types de circuits. Le premier (fig. 37) est dit à report parallèle, le second (fig. 38) à report série. Dans le report série on utilise la fonction Ji-1. On évite ainsi des portes à multiples entrées. Par contre, il faut tenir compte du retard dans l'établissement de Ji-1. Il faut donc que la largeur des impulsions d'horloge soit assez grande et la vitesse maximum de fonctionnement sera plus faible que pour le report parallèle.

Les deux schémas présentés sur les figures 37 et 38 correspondent à des compteurs-décompteurs

Article plus récent Article plus ancien